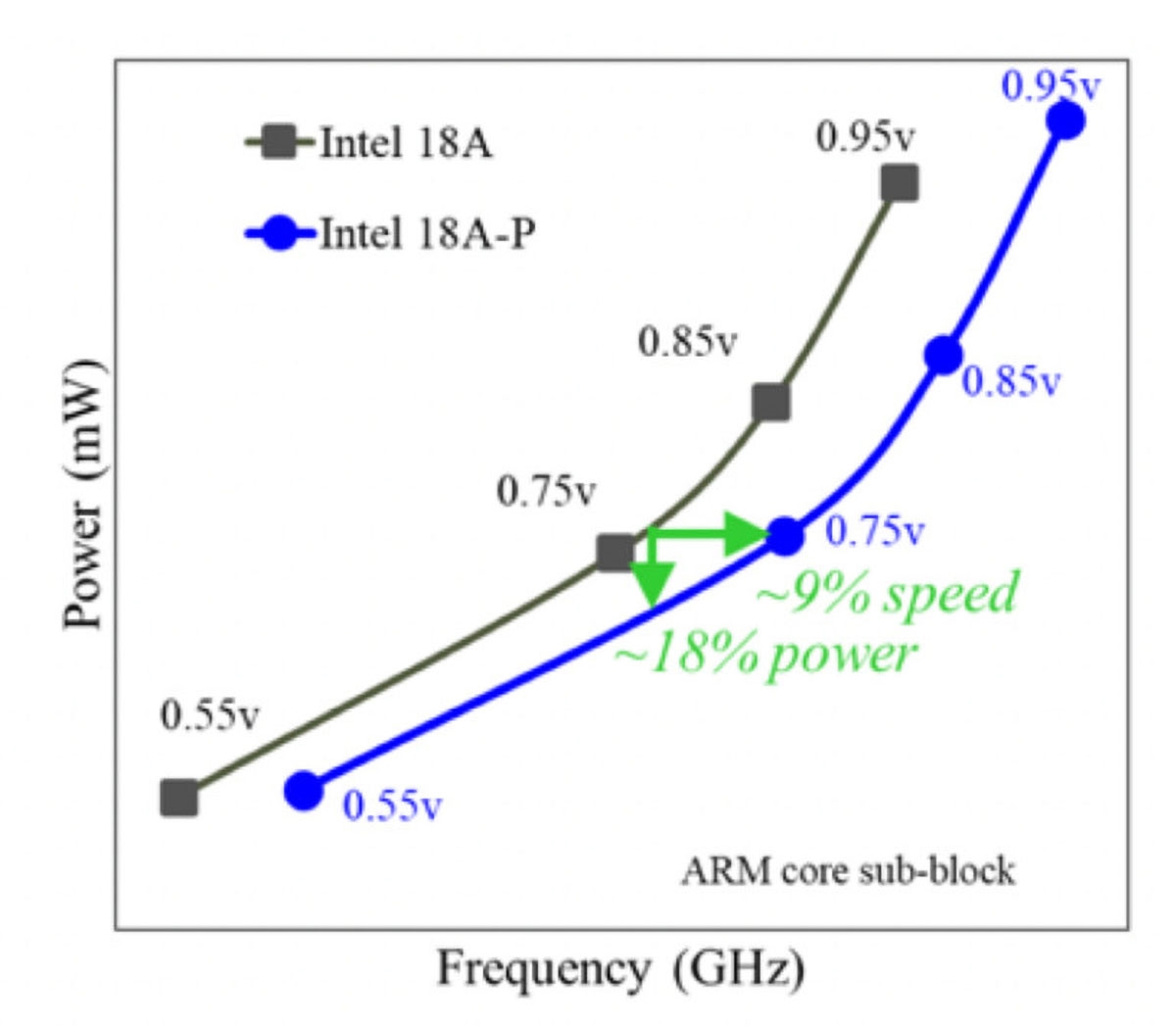

أعلنت إنتل رسميًا عن البيانات الفنية الرئيسية لعقدة عملية Intel 18A-P من خلال الورقة T1.2 في ندوة VLSI 2026 التي عقدت في هونولولو، هاواي. بالمقارنة مع عقدة Intel 18A القياسية، تحقق 18A-P زيادة في الأداء تزيد عن 9% في ظل نفس استهلاك الطاقة وتقلل من استهلاك الطاقة بأكثر من 18% في ظل نفس الأداء.

يمكن الآن تحقيق هذه الأنواع من تحسينات الأداء والطاقة، التي لا تتم رؤيتها عادةً إلا من خلال انتقالات العقد عبر الأجيال، باستخدام 18A-P بنفس الكثافة.

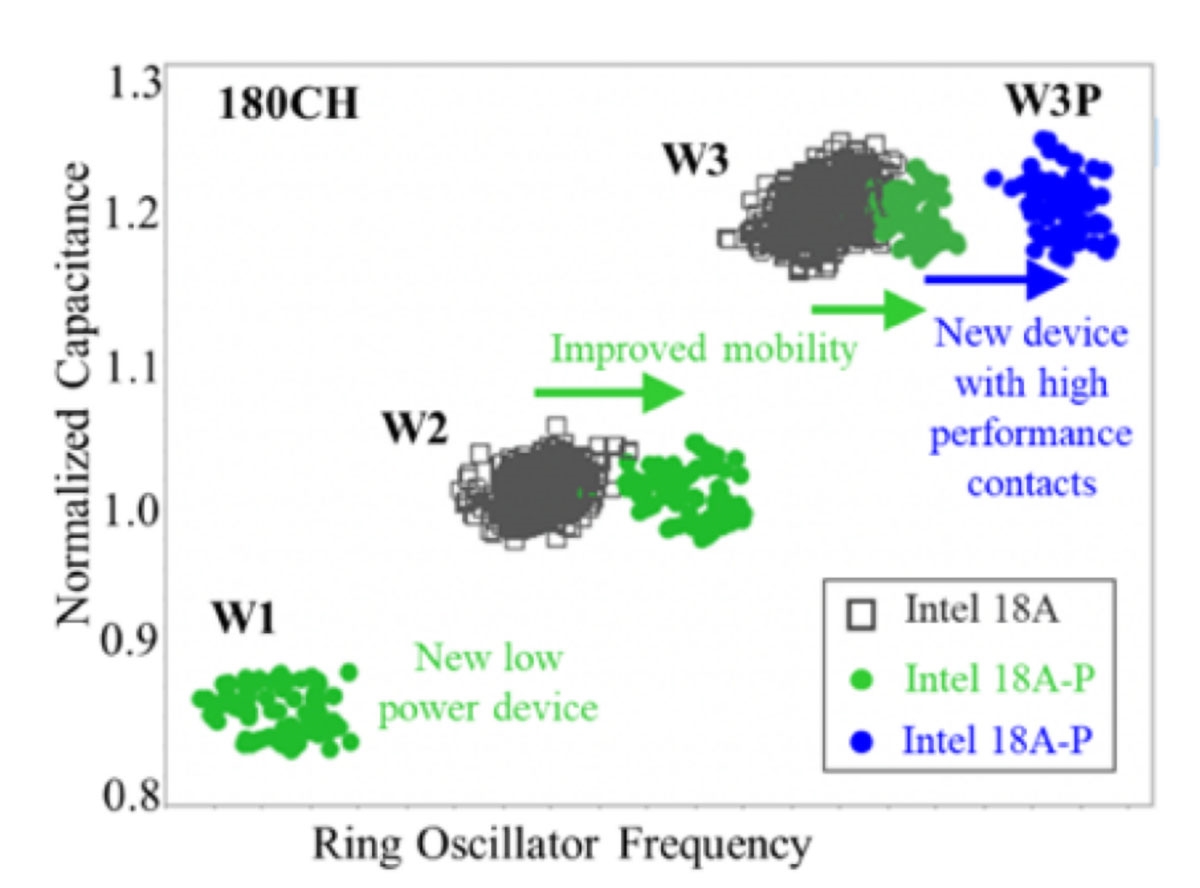

تسرد ورقة Intel الأصلية أربعة تحسينات محددة: أزواج VT المنطقية الإضافية، والتحكم الأكثر إحكامًا في زاوية إزاحة الساعة، وأجهزة جديدة منخفضة الطاقة في مكتبات عالية الكثافة (HD) وعالية الأداء (HP)، وإصدارات محسنة من أجهزة HP في كلتا المكتبتين.

قامت شركة Intel بتضييق زوايا الانحراف لـ 18A-P بحوالي 30% مقارنةً بالمعيار 18A. تم تقليل فرق الأداء بين الترانزستورات الموجودة على نفس الرقاقة بشكل كبير، وأصبح استهلاك الطاقة وخصائص الأداء أكثر قابلية للتنبؤ، كما تم تحسين إنتاجية المعلمة واتساق الشريحة في نفس الوقت.

فيما يتعلق بتبديد الحرارة، فإن المقاومة الحرارية لـ 18A-P أقل بحوالي 50% من مقاومة 18A، وتم تحسين كفاءة التوصيل الحراري بشكل كبير. يعد هذا أمرًا بالغ الأهمية بشكل خاص للتشغيل المستدام عالي التردد في سيناريوهات الحوسبة عالية الأداء، كما يستجيب بشكل مباشر لتحديات تبديد الحرارة الناجمة عن تقنية مصدر الطاقة الخلفي (PowerVia).

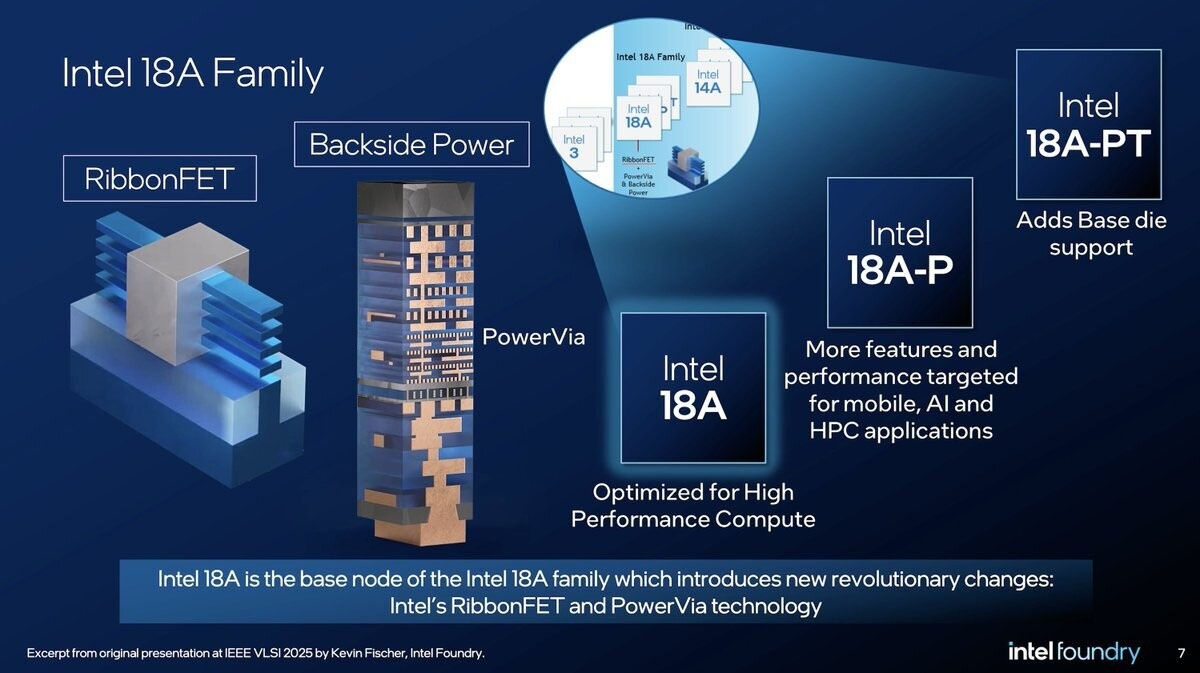

قامت Intel بشحن الإصدار 1.0 من مجموعة تصميم عملية PDK الخاصة بها لـ 18A-P إلى العملاء المحتملين لتمكينهم من بدء اختبار التحقق من الرقاقة. لا تزال هذه العملية تعتمد على بنية ترانزستور البوابة الشاملة RibbonFET وتقنية إمداد الطاقة الخلفية PowerVia، وهي نسخة محسنة الأداء من منصة 18A.

وفقًا لـ TrendForce، تقوم شركة Apple بتقييم استخدام عملية 18A-P لإنتاج شرائح السلسلة M، بينما تفكر Google في استخدام تقنية التغليف المتقدمة EMIB من Intel للترويج لمشروع TPU v8e. يمكن إطلاق المنتجات ذات الصلة في وقت مبكر من عام 2027.